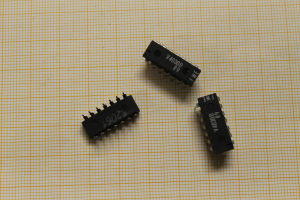

V4030 – der DDR Halbleiterschaltkreis beinhaltet vier exklusive OR Gatter mit je zwei Eingängen und positiver Logik. Der Schaltkreis wurde in zwei Varianten gefertigt. Die hier abgebildete Variante ist der V4030D mit einem DIP-14 Gehäuse. Weiterhin gab es diesen Halbleiterschaltkreis noch als V4030S – die Bauform ist dann SO-14. Das Datenblatt des V4030 ist, wie die weiteren unipolaren Logikschaltkreise V4001D, V4011D, V4012D und V4023D, in der DDR TGL 38605 mit enthalten.

V4030 – der DDR Halbleiterschaltkreis beinhaltet vier exklusive OR Gatter mit je zwei Eingängen und positiver Logik. Der Schaltkreis wurde in zwei Varianten gefertigt. Die hier abgebildete Variante ist der V4030D mit einem DIP-14 Gehäuse. Weiterhin gab es diesen Halbleiterschaltkreis noch als V4030S – die Bauform ist dann SO-14. Das Datenblatt des V4030 ist, wie die weiteren unipolaren Logikschaltkreise V4001D, V4011D, V4012D und V4023D, in der DDR TGL 38605 mit enthalten.

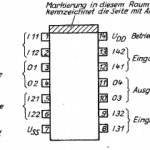

V4030 IC – Anschlussbelegung und Schaltzeichen

Der DDR Schaltkreis V4030 hat insgesamt 14 Anschlüsse. Die Belegung der Anschlüsse sowie die Eingänge und Ausgänge mit den Oder Verknüpfungen werden in den folgenden Abbildungen ersichtlich. (Quelle: TGL 38605)

|

|

Wahrheitstabelle des V4030

Die Wahrheitstabelle gibt die Verknüpfungen der Eingänge mit den Ausgängen an. Der V4030 hat die folgende Wahrheitstabelle.

| Schritt | Anschluss | ||

|---|---|---|---|

| Eingang | Ausgang | ||

| In1 | In2 | On | |

| 1 | L | L | L |

| 2 | H | L | H |

| 3 | L | H | H |

| 4 | H | H | L |

Funktionsbeschreibung des DDR Schaltkreises

Die integrierten CMOS-Logikschaltkreise sind in gepufferter Schaltungstechnik ausgeführt und entsprechen in den statischen und elektrischen Kennwerten der JEDEC Standard B Serien Spezifikation.Die Eingänge erhalten eine integrierte Dioden-Widerstandskombination als Gateschutz. Die Funktion wird in dem angegebenen Betriebsspannungsbereich garantiert.

Ausgewählte Kennwerte des DDR Schaltkreises V4030

Die CMOS Schaltkreise müssen beim Einsatz grundsätzlich gegen Überspannungsspitzen der Versorgungsspannung und der logischen Signale geschützt werden. Die folgende Tabelle zeigt die maximal zulässigen Kennwerte für die Schaltkreise V4030 sowie V4001D, V4011D, V4012D und V4023D.

| Kenngröße | Kurzzeichen | Einheit | min. | max. |

|---|---|---|---|---|

| Betriebsspannung | UDD | V | USS -0,5 | USS + 18 |

| Eingangsspannung | UI | USS -0,5 | UDD + 0,5 | |

| Ausgangsspannung | U0 | USS -0,5 | UDD + 0,5 | |

| Eingangsstrom | |II| | mA | – | 10 |

| Gesamtverlustleistung | Ptot | mW | – | 300 |

| – | 150(85°C) | |||

| Verlustleistung pro Ausgangstransistor | PV | – | 100 | |

| Lagerungstemperaturbereich | θstg | °C | -55 | 125 |

| Lastkapazität | CL | nF | – | 5 |

Bei dem DDR Schaltkreis V4030 dürfen keine logischen Eingangssignale angelegt werden, wenn die Speisespannung abgeschalten ist. Alle unbenutzten Eingänge müssen mit UDD oder USS verbunden sein.

Betriebsbedingungen des CMOS-Schaltkreises V4030

Die folgenden Angaben gelten für einen Betrieb bei -25 .. 80°C sowie für USS = 0V

| Kenngröße | Kurzzeichen | Einheit | min. | max. | Messbedingungen |

|---|---|---|---|---|---|

| Betriebsspannung | UDD | V | 3 | 15 | |

| Eingangsspannung | UI | 0 | UDD | ||

| H-Eingangsspannung | UIH | 3,5 | – | UDD = 5V UOL = 0,5V UOH = 4,5V |I0| < 1µA |

|

| 7 | – | UDD = 10V UOL = 1V UOH = 9V |I0| < 1µA |

|||

| 11 | – | UDD = 15V UOL = 1,5V UOH = 13,5V |I0| < 1µA |

|||

| L-Eingangsspannung | UIL | – | 1,5 | UDD = 5V UOL = 0,5V UOH = 4,5V |I0| < 1µA |

|

| – | 3 | UDD = 10V UOL = 1V UOH = 9V |I0| < 1µA |

|||

| – | 4 | UDD = 15V UOL = 1,5V UOH = 13,5V |I0| < 1µA |

|||

| Betriebstemperaturbereich | θstg | °C | -40 | 85 | |

| Ansteigs- und Abfallzeit des Eingangssignals | tLH tHL |

µs | – | 15 |

V4030 Schaltkreis – Datasheet – Datenblatt

Das Datenblatt (Datasheet) des Schaltkreises V4030 ist in der DDR TGL 38605 enthalten.